AMD’s upcoming Zen 6 CPU complex die (CCD) is poised to redefine high-end desktop performance with a radical departure from its predecessors. Unlike previous generations that relied on compacted cores for high core counts, the new CCD packs 12 full-performance cores—all capable of sustaining high clock speeds—into a single chiplet. This marks the first time AMD has doubled the core count on a standard CCD without sacrificing performance, pairing them with a 48MB L3 cache, a 50% increase over Zen 5’s 32MB.

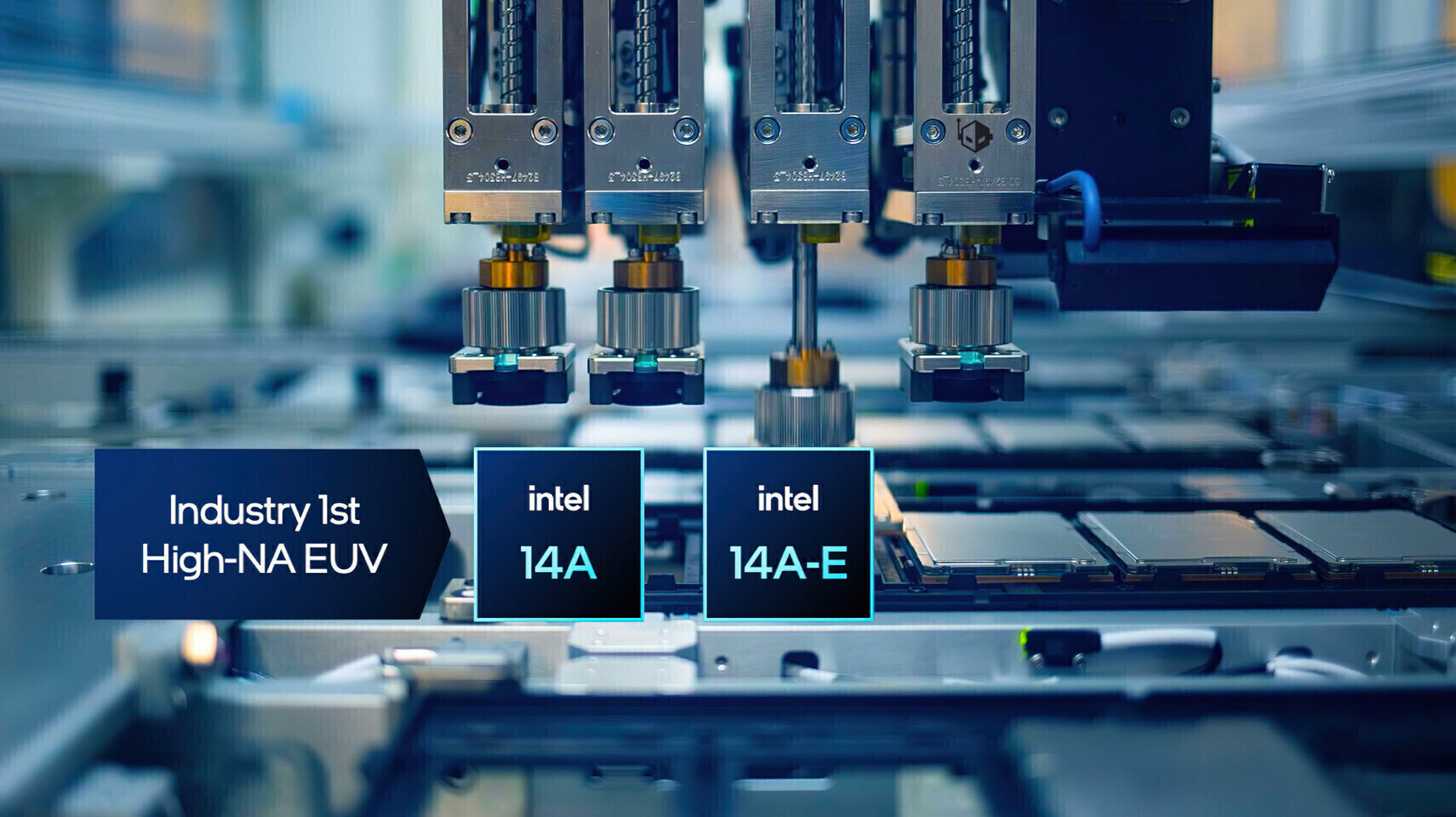

The shift doesn’t stop at core count. AMD is manufacturing the Zen 6 CCD on TSMC’s 2nm nanosheet process, a leap from the 4nm FinFET node used for Zen 5. The 2nm node promises higher transistor density, improved efficiency, and potentially better thermal performance—critical for AMD’s push into high-core-count designs. Early indications suggest the CCD will maintain a similar die size (~76mm²) to Zen 5, despite the added complexity.

A Direct Response to Intel’s Cache Strategy

AMD’s move appears tailored to counter Intel’s recent emphasis on massive last-level caches in its Core Ultra 400 series. While Intel’s Nova Lake-S processors rebalance cache allocations toward larger L3 pools, AMD is doubling down on 3D V-Cache technology. Rumors suggest future Zen 6 X3D processors could feature 144MB L3 cache per CCD, enabling up to 288MB total on desktop AM5 systems—a figure that would dwarf even Intel’s most aggressive cache designs.

Key Specs: The Zen 6 CCD in Numbers

- Core Count: 12 (all full-performance, high-clock cores)

- L3 Cache: 48MB (shared across all cores)

- Fabrication Node: TSMC 2nm nanosheet (vs. Zen 5’s 4nm FinFET)

- Die Size: ~76mm² (slightly larger than Zen 5’s 71mm²)

- Architectural Note: First CCD to feature 12 high-performance cores without compacted designs

- Future X3D Potential: Up to 144MB L3 per CCD (288MB total on AM5)

The implications for AMD’s desktop lineup are significant. While the standard CCD alone won’t define the full product stack—AMD still relies on I/O die configurations for final SKUs—the 12-core CCD suggests a foundation for Ryzen 9000-series processors with unprecedented core counts. Earlier leaks pointed to a 16-core Ryzen 9000X3D with 192MB L3 cache, and the new CCD could accelerate that timeline, particularly if paired with the larger cache pools rumored for X3D variants.

Who Benefits?

The Zen 6 CCD’s design targets two key audiences: content creators and enthusiasts demanding raw multi-threaded performance, and gamers who may benefit from the 3D V-Cache enhancements. For the former, the 12-core CCD could underpin a Ryzen 9 with 24 threads, competing directly with Intel’s 16-core Core i9-14900K while offering superior single-threaded performance. Gamers, meanwhile, may see the first Ryzen 9000X3D models with 288MB L3 cache, potentially closing the gap with NVIDIA’s RTX 50-series GPUs in ray-traced workloads.

Thermal and power constraints remain a question mark. While AMD hasn’t disclosed TDP figures for Zen 6, the 200W TDP of the Ryzen 9000X3D suggests aggressive power management. The 2nm process could mitigate some inefficiencies, but high-core-count designs will still require robust cooling—especially if AMD pushes clock speeds beyond the 5.6GHz boost seen in the Ryzen 7 9850X3D.

Looking Ahead: A Shift in the Desktop Landscape

AMD’s Zen 6 CCD isn’t just an incremental upgrade; it’s a strategic pivot. By doubling core count and cache while adopting a cutting-edge process node, AMD is positioning itself to challenge Intel’s dominance in both productivity and gaming. The inclusion of 3D V-Cache as a standard feature—rather than a niche offering—could redefine how AMD markets its high-end chips, potentially making X3D a default for flagship models.

One unanswered question is whether AMD will extend the 12-core CCD across its entire lineup or reserve it for the top tier. Past patterns suggest a tiered approach, with Ryzen 5 and Ryzen 7 models sticking to 6-core and 8-core CCDs, respectively. However, the introduction of a 12-core standard CCD could pressure AMD to rethink its roadmap—especially if TSMC’s 2nm yields prove as efficient as hoped.

Availability remains unclear, but leaks suggest Zen 6 could debut in late 2026 or early 2027, coinciding with DDR6 memory maturing to support speeds up to 17,600 MT/s. If AMD delivers on its promises, the Zen 6 CCD could mark the beginning of a new era in x86 performance—one where core count, cache, and process node advancements converge to outpace Intel’s traditional strengths.