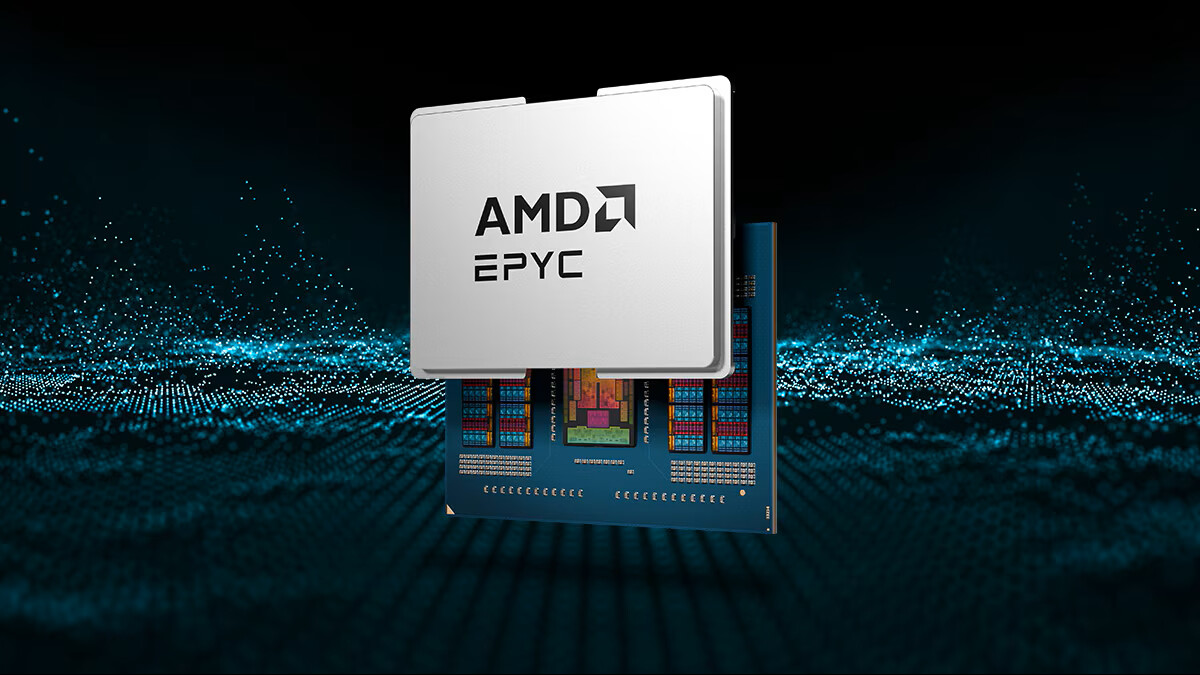

Cloud providers managing shared CPU resources often need to enforce strict performance boundaries between tenants. AMD’s upcoming Zen 6 microarchitecture introduces advanced Platform Quality of Service (PQOS) extensions designed to address this challenge, offering deeper control over bandwidth allocation and privilege-level associations.

The new features—Global Bandwidth Enforcement (GLBE), Global Slow Bandwidth Enforcement (GLSBE), and Privilege-Level Zero Association (PLZA)—expand on existing PQOS mechanisms by allowing system software to regulate L3 cache bandwidth across multiple QoS domains. This shift from per-domain granularity to a unified control model could improve workload isolation in large-scale deployments.

Global Bandwidth Enforcement (GLBE) lets administrators set external L3 bandwidth limits for groups of cores spanning several traditional QoS domains, creating a shared ceiling for specific Classes of Service (CoS). Similarly, Global Slow Bandwidth Enforcement (GLSBE) applies the same logic to memory explicitly marked as 'slow,' ensuring consistent performance even when slower DRAM modules are in use. Both features rely on model-specific registers for precision tuning.

Privilege-Level Zero Association (PLZA) introduces a new layer of security and monitoring by automatically linking highly privileged execution (CPL=0) to predefined CoS or Resource Monitoring Identifiers (RMID). Unlike previous implementations tied to individual threads, PLZA allows the hardware to override thread-level associations dynamically, enabling tailored resource limits for system software like host OS kernels or hypervisors running with AMD SVM.

While these extensions promise finer-grained control over multicore performance, their real-world impact will depend on how widely they’re adopted in cloud environments. Early testing suggests they could be particularly valuable for providers leasing out CPU cores to multiple tenants, but long-term effectiveness remains unconfirmed.