The global semiconductor market is entering a phase of heightened competition, with TSMC and Samsung Foundry solidifying their dominance in high-end chip manufacturing. Against this backdrop, Intel’s foundry arm is making a strategic hire that could mark a turning point in its ability to challenge for leadership in advanced process nodes.

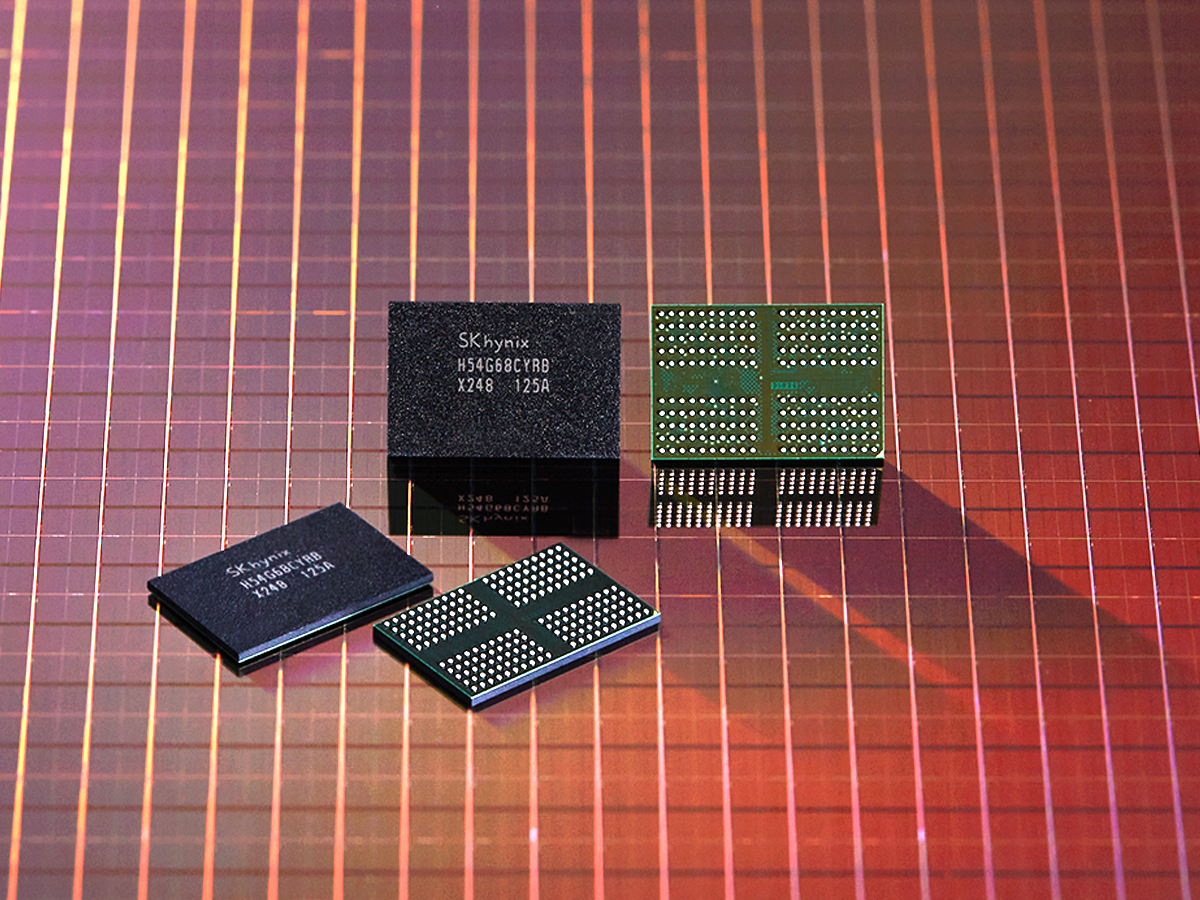

Intel has appointed an executive with nearly three decades of experience—most recently at Samsung—to lead its foundry operations. This individual brings deep expertise in developing processes for 3nm and below, including advanced packaging and extreme ultraviolet (EUV) lithography. The hire suggests Intel is doubling down on closing the gap with competitors, particularly in areas where yield and time-to-market are critical.

Key aspects of this shift include

- Intel’s foundry business aims to capture 20% of the global market by 2027, up from roughly 15% today. This ambition hinges on scaling production for high-NA EUV and multi-die solutions.

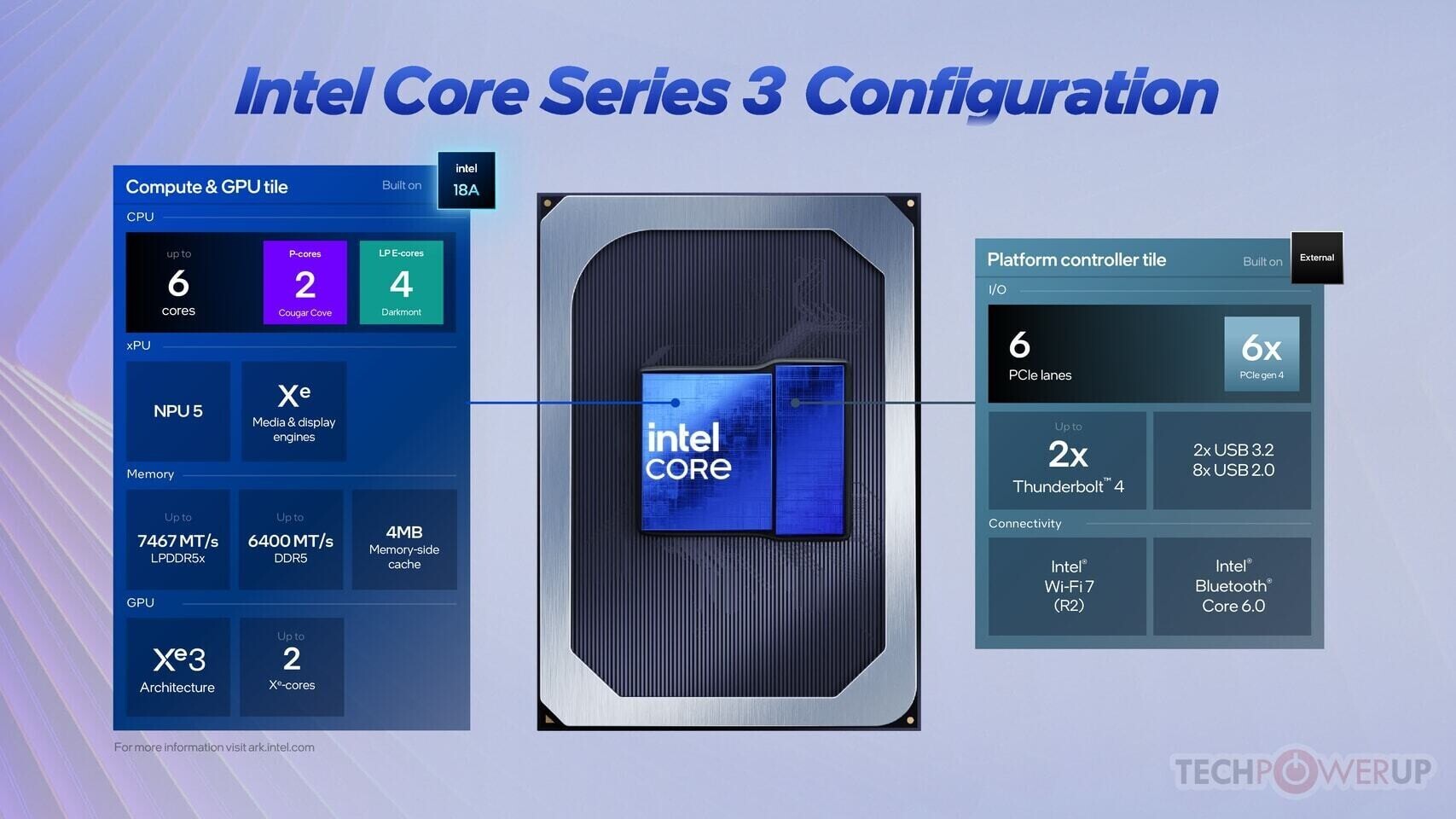

- The company is currently ramping its 18A node while competitors have already secured significant orders for leading-edge designs at 3nm and below.

- Improving yield rates and refining process nodes will be central to Intel’s strategy, with a focus on addressing customer demands for performance-per-watt efficiency in next-generation platforms.

The leadership change could also indicate a shift toward more customer-driven innovation, addressing historical concerns about Intel’s competitiveness in advanced packaging. For system designers and PC builders, this means closer attention to Intel’s roadmap, which will directly influence the performance characteristics of future hardware.

However, challenges remain. Supply constraints continue to plague Intel’s foundry operations, and the speed at which it can bridge its gap with TSMC in volume and yield will determine whether this strategic move translates into tangible market share gains or merely another step in a longer race for leadership in high-end chip manufacturing.